小讲堂 - EtherNet/IP | 第7讲:EtherNet/IP硬件接口(二)

罗克韦尔自动化及软件部门技术顾问王宏善

2014-05-22 罗克韦尔自动化

4以太网通讯接口设计

4.1以太网电路原理

以太网控制器是EtherNet/IP通信适配器中一个非常重要的物理部件,它实现以太网的数据链路层协议。为了保证设备能够很好地满足工业应用的要求,所选用的以太网控制器需具备以下一些特点:能在工业环境中运行,对高温低温、噪声、震动等有一定的抵抗能力;支持全双工通讯;支持10Mbit/s或100Mbit/s传输速率等。S3C2410A没有内置的以太网控制器,本文采用Cirrus Logic公司开发的CS8900A—IQ3作为EtherNet/IP通信适配器的以太网控制CS8900A-IQ3主要特点是:lOMbit/s的传输速率、支持全双工运作模式、内建缓冲区提供传送接收讯框(Frames)、可对错误的封包自动排除等;此外,其特有的PacketPagel”结构可以自动调适网络交通的模式以及系统可用的资源。以太网通讯接口设计中还需使用隔离变压器,其主要作用是把设备的有源部分和其网络接口隔离开,以避免干挠网络的运行。隔离变压器应该提供尽可能高的共模抑制比,ODVA/CI推荐采用在30HZ时共模抑制比在59dB以上的隔离变压器。

4.2以太网芯片CS8900A-IQ3功能描述

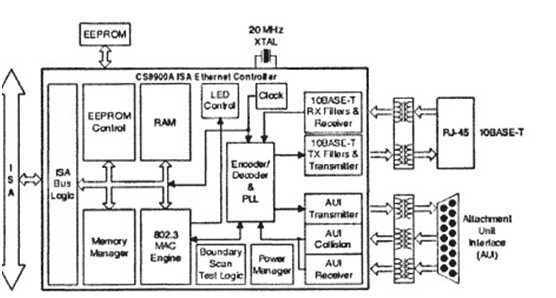

图3 CS8900A-CQ3功能图

在电源开启或硬件复位后,CS8900A--IQ3要传送或接收封包时必须先芯片内部的组态、控制寄存器作参数的设置,比如说:存储器的基底位址、以太网络的物理位址、什么形态的讯框可以被接收和底层媒体介面是什么等等设置。这些参数的来源有两个地方:一个是由host透过ISA汇流排写入CS8900A-CQ3,另一个则是通过外部EEPROM自动载入进来。在所有寄存器设置完毕后CS8900A-CQ3便可进行相关动作.基本上CS8900A—CQ3的主要运作有两个部份:封包传送、封包接收。

封包传送:

在CS8900A-CQ3的封包传送过程中有两个阶段:

(1)封包传送第一个阶段:

主机将封包数据搬移至CS8900A—C03的缓冲存储器,这样子的搬移动作是在主机发出传送命令时所发生的。传送命令是要通知CS8900A-CQ3有封包数据需要被传送,并且何时要被传送(可在CS8900A-CQ3缓存器内设置成5,381,1021或是所有bytes被传送出去),以及如何被传送出去(有无CRC、添加的位数据等等)。在传送命令发出后,传送的长度也要告知,这样CS8900A-CQ3需要多少的缓冲空间才可被配置出来。当足够的缓冲空间被配置出来后,主机便可透过I/O模式或是Memory的模式,将封包数据写入CS8900A-CQ3的内部存储器。

(2)封包传送第二个阶段:

CS8900A—CQ3将封包数据转换成以太网络讯框,之后送到网络CS8900A—CQ3会在传送缓冲空间累积到足够的数据(先前在CS8900A—CQ3缓存器内设置成5,381,1021或是所有bytes被传送出去等情形),便马上传送出去。被传送出去的数据依照IEEE802.3以太网络讯框的格式(如下图所示)传送到网络上,以太网络讯框的最大数据酬载量(Payload)为1500 Bytes,最小为46 Bytes,如果上层封包数据量(包含CRC即Cyclic Redundancy Check,也就是FCS即Frame CheckSequence)小于46Bytes,那么CS8900A-CQ3会依照缓存器的设定来决定是否要填加位以补足讯框的最小量,最后再加上4 Bytes FCS送出。

封包接收:

(1)封包接收的第一个阶段:

CS8900A-CQ3接收以太网络讯框后,将讯框存放在内部芯片的内存中,将前导的字节(preamble)以及Start of Frame启始字节移除掉,然后利用地址过滤器比对是否该接收的讯框目的地的地址与网络芯片所设置的地址相同,如果正确的话,便存放在CS8900A—CQ3内部存储器,然后CS8900A-CQ3检查CRC以及相关设定, 以更进一步确认讯框之无误,然后通知微处理器讯框已被接收的事件。

(2)封包接收的第二个阶段:

5串行通讯接口设计

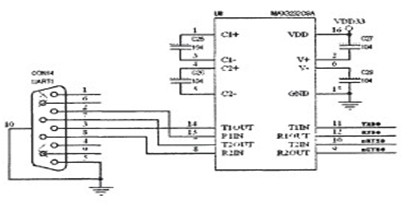

S3C2410A内置3通道UART控制器,可以基于DMA模式或中断模式工作,支持5bits、6bits、7bits或者8bits串行数据发送/接收。本文采用MAXIMG公司为嵌 入式低功耗应用设计的MAX3232作为串口通讯收发器,MAX3232工作电压为3.3V,输出电平完全兼容RS232工业标准,最大收发速率为120kbps。本文设计EtherNet/IP通讯模块可通过串口直接与PC机连接,并使用串口为程序调试打印信息。串行通讯接口如图4所示:

图4 RS232接口电路图

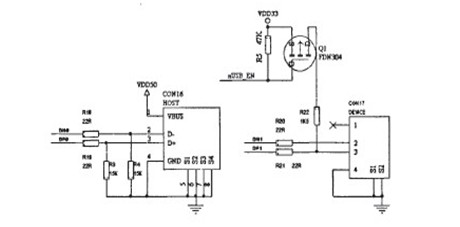

6 主从USB接口设计

包括一个USB主机端口和一个USB设备端口。主机端口连接外围设备,如鼠标等,设备端口用于连接PC机。S3C2410A芯片内集成了USB主从控制器,因此,电路上只需加效应管驱动即可构成完整的USB电路,无需加任何USB芯片,这大大简化了电路设计。

图5 USB接口

7 外部I/0扩展接口设计

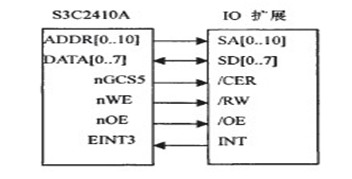

EtherNet/IP通信适配器采用总线模式与多个数字I/O模块相连接,在通信适配器内部给每个I/O模块分配了一个的物理地址,S3C2410A通过具体的物理地址直接读写I/O模块的数据。在S3C2410A与I/O接口之间采用了总线驱动器件,一方面提高主控制器的总线驱动能;另一方面可以隔离S3C2410A系统总线与外部I/O模块直接连接。外部扩展I/O接口原理如图4.12所示。图8中/CER为外部I/O模块的片选信号,/RW输出型I/O的写信号,/OE为输入型I/O的读信号, T为I/O模块产生的中断信号。对于比较重要的I/O可以采用中断的方式进行读写,正常情况下,以查询方式读写I/O数据。

图6外部扩展IO接口原理

小讲堂 - EtherNet/IP | 第1讲:

EtherNet/IP网络和CIP协议浅析

小讲堂 - EtherNet/IP | 第2讲:

CIP Sync 技术浅析

小讲堂 - EtherNet/IP | 第3讲:

CIP Motion 技术浅析

小讲堂 - EtherNet/IP | 第4讲:

CIP Safety 技术浅析

小讲堂 - EtherNet/IP | 第5讲:

EtherNet/IP性能分析

小讲堂 - EtherNet/IP | 第6讲:

EtherNet/IP硬件接口设计(一)

与我们联系,请点击这里

与我们联系,请点击这里